NAND gate: Difference between revisions

No edit summary |

No edit summary |

||

| Line 33: | Line 33: | ||

As NOR gates are also functionally complete, if no specific NAND gates are available, one can be made from NOR gates using NOR logic. | As NOR gates are also functionally complete, if no specific NAND gates are available, one can be made from NOR gates using NOR logic. | ||

== See also == | |||

* [[AND gate]] | |||

* [[OR gate]] | |||

* [[NOR gate]] | |||

* [[XOR gate]] | |||

* [[XNOR gate]] | |||

* [[Inverter|Inverter (NOT gate)]] | |||

* [[IMPLY gate]] | |||

* [[NIMPLY gate]] | |||

[[Category:Logic gates]] | [[Category:Logic gates]] | ||

Revision as of 18:43, 8 November 2023

| NAND gate truth table | ||

|---|---|---|

| Input | Output | |

| A | B | A NAND B |

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

In digital electronics, a NAND gate is a logic gate which produces an output of false when all its inputs are true; thus the outputs are the complement of the AND gate. A LOW (0) output results only if all the inputs to the gate are HIGH (1); if any input is LOW (0), a HIGH (1) output results.

The NAND gate is significant because any Boolean function can be implemented by using a combination of NAND gates. This property is called "functional completeness". It shares this property with the NOR gate. Digital systems employing certain logic circuits take advantage of NAND's functional completeness.

Logic

The function NAND(a1, a2, ..., an) is logically equivalent to NOT(a1 AND a2 AND ... AND an).

A two-input NAND gate can be expressed in Boolean logic as .

Another way of expressing A NAND B is , where the symbol signifies AND and the bar signifies the negation of the expression under it: in essence, simply .

Functional completeness

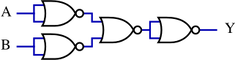

The NAND gate has the property of functional completeness, which it shares with the NOR gate. That is, any other logic function (AND, OR, etc.) can be implemented using only NAND gates.

As NOR gates are also functionally complete, if no specific NAND gates are available, one can be made from NOR gates using NOR logic.